计算机组成原理——2.1 存储系统

一、存储器的层次结构

graph TB CPU --> Cache(Cache高速缓冲储存器) Cache --> A(主存/内存) A -->B(磁盘/辅存) B -->C(U盘-磁带-光盘/外存)

-

从上到下:容量从小到大、速度,价格从大到小

-

性能更高的,还会将cache分为L1(一级cache)L2( 二级cache)等等,通常来说,L1最快。cache成本比内存大得多。

-

主存&辅存:实现虚拟存储系统,解决主存容量不够的问题。

-

Cache&主存:解决了主存与CPU速度不匹配的问题。

1、按层次分类

graph LR A(按层次分类) subgraph memory B(高速缓存--cache) C(主存储器--主存 - 内存) end D(辅助存储器--辅存 - 外存) E(可直接被CPU读写) A -->B A -->C A -->D B -->E C -->E

2、存储介质

- 半导体存储器(主存,Cache)

- 磁性材料存储器(磁盘,磁带)

- 光存储器,以光介质存储信息(光盘)

3、存取方式

-

随机存储器(Random Access Memory,RAM)

读写任何一个存储单元所需要的时间都相同,与存储单元所在物理位置无关。如内存条

-

顺序存储器(Sequential Access Memory,SAM)

读写一个存储单元所需的时间取决于存储单元所在位置。如磁带

-

直接存取存储器(Direct Access Memory,DAM)

既有随机存储特性,也有顺序存储特性。先直接选取信息所在的区域,然后按顺序的方式存储。如:机械硬盘

-

相联存储器(Associative Memory)即可以按内容访问的存储器(Content Addressed Memory,CAM)

可以按照内容检索到存储位置进行读写。快表[1]就是一种相联存储器

-

顺序存储和直接存储的存储器统称串行访问存储器:

读取某个存储单元所需时间与存储单元的物理位置有关。

4、信息的可更改性

- 读写存储器(read/write Memory)== 可读也可写(磁盘,内存,cache)

- 只读存储器(Read Only Memory)== 只读,不可写(CD-ROM,BIOS存储的ROM)要写入比较麻烦,需要先擦除再写入。

5、信息的可保存性

- 易失性存储器(主存,cache):断电后存储信息就消失了

- 非易失存储器(磁盘,光盘):断电后信息还保留

- 破坏性读出(DRAM):信息读出后,原存储信息被破坏。DRAM读出数据后需要进行重写

- 非破坏性读出(SRAM,磁盘,光盘):信息读出后,原本信息不会被破坏

6、存储器性能指标

-

存储容量:存储字长(MDR位数) x 字长(如:1M x 16位)

-

单位成本:每位加个 = 总成本 / 总容量

-

存储速度:数据传输率 = 数据的宽度 / 存储周期

-

存取时间Ta:从启动一次存储器操作到完成该操作所经历的时间,分读出时间和写入时间。

-

存取周期Tm:存储器进行一次完整的读写操作所需的全部时间。(也就是连续两次独立访问存储器操作,所需的最小时间间隔)

-

主存带宽Bm:又称数据传输率。表每秒从主存进出心理的最大数量,单位:字/秒、字节/每秒(B/s)、位/秒(b/s)

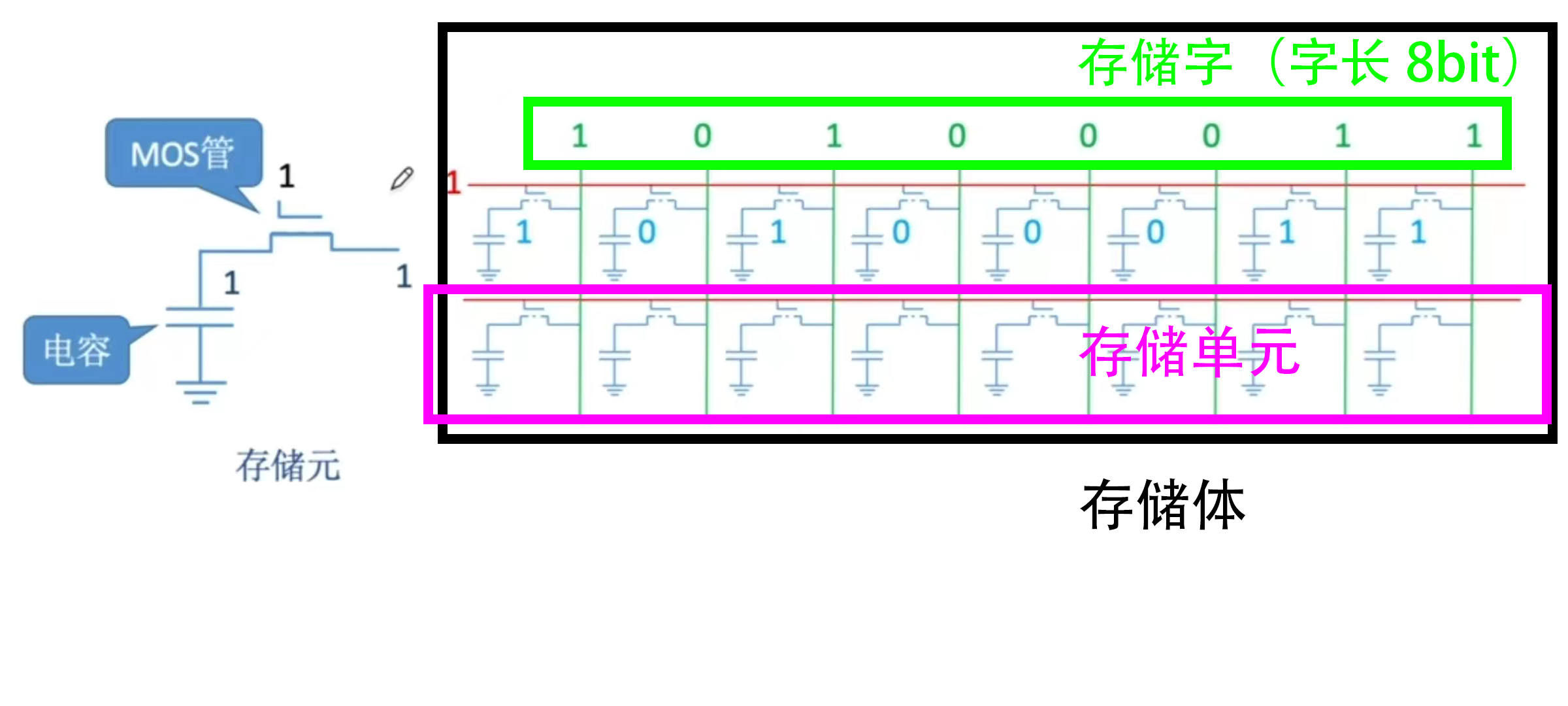

二、主存储器基本组成

由电容与MOS关组成

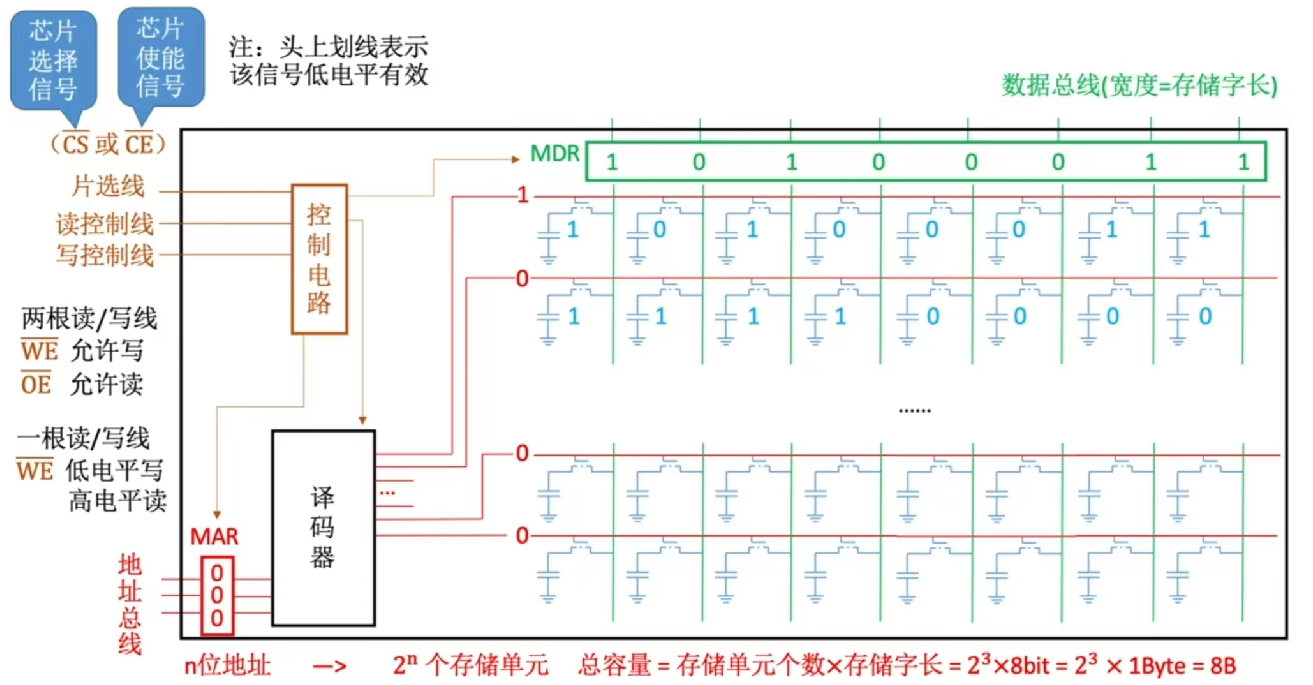

我们使用译码器,使用n位地址找到2^n个存储单元里对应的存储信息。地址由MAR存储。CPU通过地址总线连接MAR。

CPU给MAR一个地址,通过译码器找到对应地址的存储单元,将其数据通过数据总线(位线)输出给MDR,MDR吧数据给CPU。数据总线的宽度 = 存储字长

- 总容量 = 存储单元个数 * 存储字长

其中,MAR和MDR需要通过控制电路和译码器驱动器,可以理解为负责稳定输出。只有MAR和MDR里的数据存储稳定之后,控制电路才会打开通路的开关,让数据在总线上进行传输。

片选线负责在多个存储芯片中,选择其中一个存储芯片,在里头读取数据。

存储芯片总结一共由于五类引脚:

-

地址线

-

数据线

-

片选线

-

读写控制线

-

供电引脚与接地引脚

寻址

按字节寻址

按字寻址

- 字地址算术左移一定位数,即可转换为对应的字节地址

按半字寻址

按双字寻址

三、SRAM & DRAM

-

DRAM,Dynamic Random Access Memory,即动态RAM

SRAM,Static Random Access Memory,即静态RAM

-

DRAM用于主存,SRAM用于Cache

-

上述介绍的 “主存储器基本组成” 就是DRAM。

| 类型特点 | DRAM(常用主存) | SRAM(常用cache) |

|---|---|---|

| 存储器 | 栅极电容 | 双稳态触发器 |

| 是否破坏性 | 电容放电时信息被破坏,是破坏性读出,读出之后应有重写操作。也称 “再生” 。 | 读出数据的时候,触发器保持状态稳定,非破坏性读出,无需重写。 |

| 读写速度 | 更慢 | 更快 |

| 集成度&成本 | 集成度高,成本低 | 集成度低,成本高 |

| 是否易失 | 是,断电后信息消失 | 是,断电后信息消失 |

| 需要刷新 | 需要,存储介质是电容 | 不需要,存储介质是触发器 |

| 送行列地址 | 分两次送 | 同时送 |

| 功耗&发热量 | 功耗低,发热量小 | 功耗高,发热量高 |

-

DRAM存储单元使用的MOS管比SRAM更少,在芯片面积不变的情况下,DRAM集成度更高。

-

核心区别:存储元不一样

3.1 DRAM刷新

-

刷新的概念

-

刷新一次的时间间隔:

DRAM使用的电容存储信息,大概2ms后信息会消失,所以DRAM每2ms就需要刷新一次。

-

每次刷新多少个存储单元:

由于DRAM存储器需要刷新,如果我们有20根选线,就有2^20 = 1M根选线。如果全部接在一个译码器,难度会很大。

此时我们把这个译码器拆分成两个,为(行地址译码器)和(列地址译码器),每个译码器只需要处理一半的地址,即2^10 = 1k = 1024根选线,这样就可以把存储单元排列成2^{n/2} x 2^{n/2}的存储单元矩阵。

使用行列地址可以减少选通线的数量

-

-

如何刷新?

所以每次刷新的时候,以行为单位,每次刷新一行存储单元。

这里有硬件的支持,由存储器独立完成,不需要CPU控制。

读出一行的信息之后就重新写入。

由于刷新一次类似于一次读操作,所以时间上占用一个读或写周期。

-

刷新的思路

-

思路一,分散刷新:

每次读写完都刷新一行

-

思路二,集中刷新:

2ms内集中安排一块时间全部刷新。那就会出现有一段时间专门用于刷新,无法访问存储器,称为访存 “死区”。

-

思路三,异步刷新:

2ms内每行刷新一次即可,那每隔2ms就会出现一次 “死时间”(可以理解为分散了死区),在这期间,CPU无法访问。可以在译码阶段刷新。

-

-

送行列地址:

- 因为DRAM使用了两个译码器,所以我们使用地址线复用技术,也就是说,每次传输一半的地址给其中一个译码器即可先接受行地址,再接受列地址,分两次传输地址,给两个译码器。我们就可以减少一半的地址线,芯片引脚也会更少。

- SRAM因为集成度更低,所以地址我们同时传输即可

-

现在主存芯片通常使用

SDRAM芯片,

四、只读存储器ROM

RAM芯片断电后数据会消失(易失性的),而:

ROM芯片,断电后数据不会消失(非易失性的)。

ROM还可以细分为:MROM、PROM、EPROM、flash闪存、 SSD

很多ROM也具有 “随机存储” 特性。

1、MROM

MROM(Mask Read Only Memory),掩模式只读寄存器

由厂家直接写入信息,只能读出,之后任何人不可重写

可靠性高、灵活性差、生产周期长,只适合批量生产

2、PROM

PROM(Programmable Read Only Memory),可编程只读存储器

用户可以用专门的软件写入信息,写一次之后就不可更改

3、EPROM

EPROM(Erasable Programmable Read Only Memory)

允许用户写入信息,之后可以擦除数据,可进行多次重写

4、UVEPROM

UVEPROM(Ultraviolet rays),可以使用紫外线照射8-20分钟,擦除所有信息

5、EEPROM

第一个E表示的是Electrically,也就是说,可以使用电擦除,擦除特定的字。

6、FLASH MEMORY

Flash Memory,闪速存储器(比如U盘、sd卡),从EEPROM发展来的。断电后可以保存信息,且可以进行多次快速擦除重写。

由于闪存需要先电擦除再写入,所以闪存的 “写” 要比 “读” 来的更慢。

每个存储元只需要一个MOS管,位密度要比RAM高。

7、SSD固态硬盘

由控制单元+存储单元(flash)组成。

与闪存的核心区别在于:控制单元不一样。

但是由于存储介质类似,可以进行多次快速擦除重写。

SSD速度快、功耗低、价格高,目前个人电脑常用SSD取代传统的机械硬盘。

手机辅存也是用的FLASH芯片。相比SSD使用的芯片,集成度高,功耗低,价格贵

五、计算机内重要的ROM

graph TB subgraph 主机 A[主存RAM //+ROM] subgraph CPU B(运算器) C(控制器) end end

CPU的任务是到主存中取指令,然后去运行。主存RAM中存放着指令与数据。而断电后,RAM数据全部丢失。

所以CPU开机的时候,里头是没有存放指令的。需要把操作系统、应用程序相关的指令、数据,重新调入主存。

而我们知道,操作系统是安装在辅存里面的。如何开机,也是需要CPU执行开机指令。但此时CPU里头完全没有指令。

所以CPU开机的时候,就需要在主板上的ROM芯片读取开机的指令。这块ROM就是BIOS。

- 主板上BIOS芯片(ROM),存储了自举装入程序,负责引导装入操作系统(开机)

逻辑上来说,主存由RAM(内存)+ROM(BIOS)组成,且二者通常统一编址。主板上ROM也是 “主存” 的一部分。

六、双端口RAM & 多模块存储器

-

存取周期:存取(启动存取 -> 存取完)的时间 + 恢复(存取完 + 下次存取之前)的时间

也可以表示成:可以连续读写的最短时间间隔

- 注:DRAM的恢复时间比较长,有可能会是存取时间的几倍(SRAM的恢复时间比较短)

每次读取完数据,都需要一段时间恢复。如果此时多核CPU都需要访存,那是不是每个CPU都需要等待RAM的恢复时间,才能进行下一次的存取?且即使是单核CPU,读写数据的速度比主存快很多,主存恢复时间太长了该怎么办?

这里就使用到双端口存储器

6.1 双端口RAM

-

作用:优化多核CPU访问一根内存条的速度,可以通过两个端口

-

需要有两组完全独立的数据线、地址线、控制线

-

两个端口同时操作主存时:

- 两个端口同时对不同的地址单元存数据

- 两个端口同时对同一个地址单元读出数据

- 两个端口同时对同一个地址单元写入数据(会造成写入错误)

- 两个端口同时对同一个地址单元,一个写入,一个读出(会造成读出错误)

- 解决方案:

- 把

busy信号置0,由判断逻辑决定暂时关闭一个端口(被延时),未被关闭的端口正常访问,被关闭的端口延长很小一段时间后可以再次访问。

- 把

6.2 多体并行存储器

CPU读写速度比内存快很多,而内存每次读写过后,需要一段恢复的时间。当CPU需要连续读取的时候,就必须等待内存的恢复时间。所以可以用上多体并行存储器

多体并行存储器可以理解为使用了多个存储体(每个内存条大小一致,假设我们使用四个存储体)

CPU访存的时候,一定需要一个地址。有以下两种编址模式

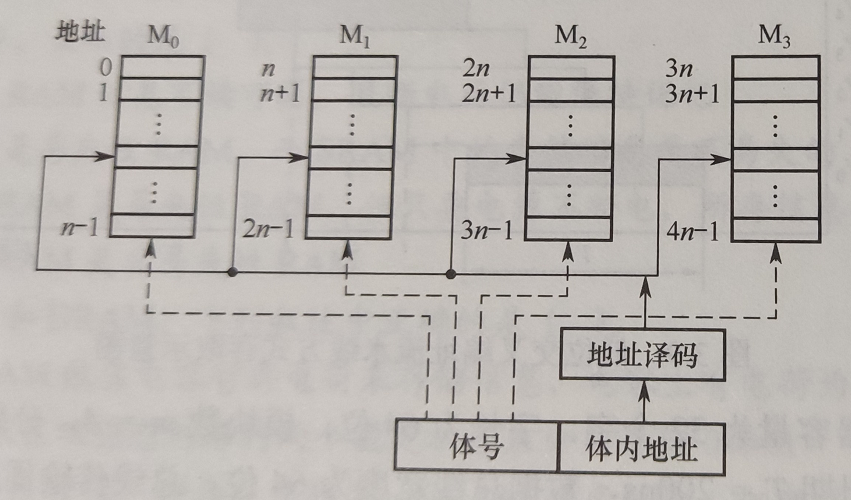

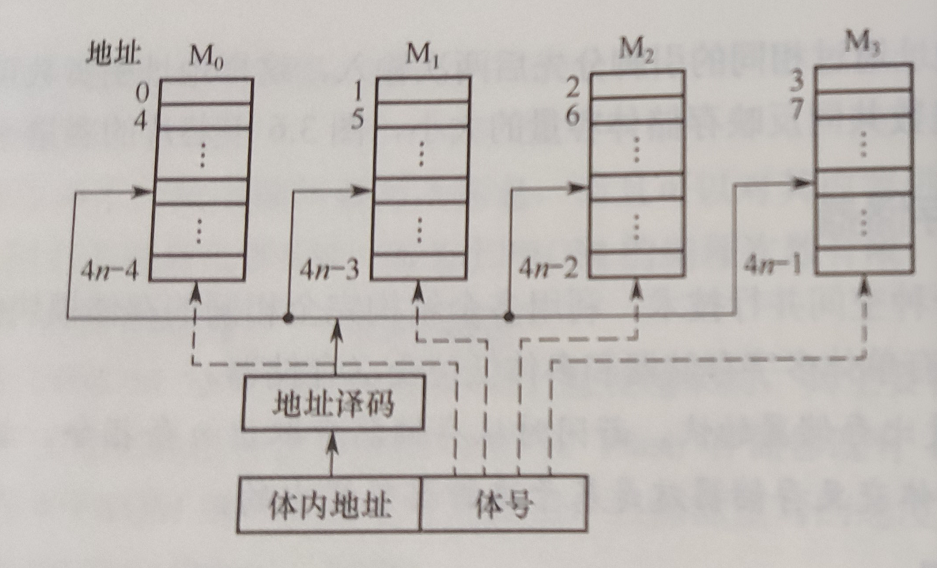

-

高位交叉编址的多体存储器

假设说我们用的八位地址,那我们就会用最高位来区分我存在第几个存储体里(比如最高两比特位共有四种状态)

- 看图可知,高位内模块地址是连续的,存取方式仍然是串行存储。仍然是顺序存储器

- 高位交叉的方式下,总是把低位的体内地址送到由高位体号确定的模块内进行译码。

- 访问一个连续主存块时,总是先在一个模块内进行访问,等到这个模块访问结束之后才转到下一个模块进行访问。

- CPU总是按顺序访问存储模块,各个模块不能被并行访问,所以不能提高存储器的吞吐率

-

低位交叉编址的多体存储器

假设说我们用的八位地址,那我们就会用最低位来区分我存在第几个存储体里(比如最低两比特位共有四种状态)

-

看图可知,每个模块按照 “模m” 交叉编址,模块号 = 单元地址 % m。

-

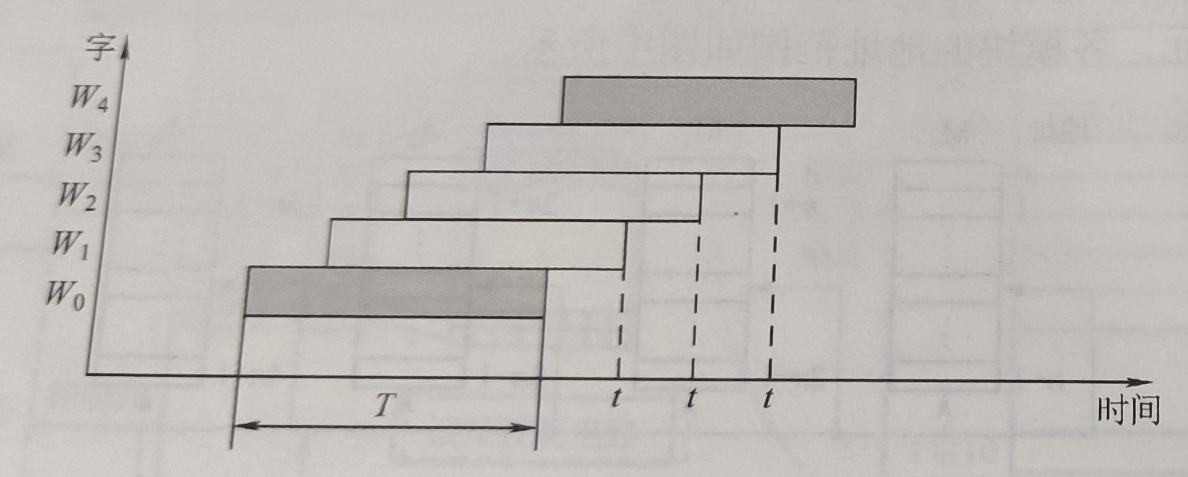

低位交叉方式下,总是把高位的体内地址送到由低位体号确定的模块内进行译码。程序连续放在相邻的模块中,因此称这种编址方式的存储器叫交叉存储器。可以在不改变每个模块存储周期的前提下,使用流水线并行存取,提高存储器的带宽。

- 如果单模块存取周期为T,总线传送周期为r,实现流水线存储,存储器交叉模块数m(交叉存储度) 应该大于等于

T/r。以保证启动某个模块后的m*r的时间内要再次启动模块的时候,这个模块已经存取完毕,并已经度过了内存的恢复时间。 - 存取周期为T,存取时间为r,为了流水线不间断,保证模块数量为

m>=T/r。

- 如果单模块存取周期为T,总线传送周期为r,实现流水线存储,存储器交叉模块数m(交叉存储度) 应该大于等于

-

这样下来,连续存取m个字所需要的时间为:

$$

t1 = T + (m-1)r

$$ -

而顺序方式连续读取m个字所需要的时间为:

$$

t2 = mT

$$ -

综上所述,低位交叉存储器的带宽得到了大幅度的提高(如下图)

-

类似数组等等数据,或者编写的指令代码,其数据存放方式就是连续的存储(除了指令跳转部分)。所以连续存取的速度提升对于计算机来说很有意义。

6.3 单体多字存储器

多体并行存储器就是,每个模块都有相同的容量和存储速度,是互相独立的。CPU可以自由选择在哪个存储体的哪个位置读取数据。

各个模块都有独立的读写控制电路、地址寄存器和数据寄存器等等。可以并行、交叉地工作。

单体多字存储器相当于做了一个合并。共用一套读写控制电路、地址控制器和数据寄存器(类似位拓展)。

每次可以读取一整行的数据

设每个存储单元,存储m个字

总线宽度也为m个字

一次并行即可读出m个字

缺点:指令和数据在主存内必须是连续存放的。一旦遇到转移指令或者操作数不能连续存放,提速的效果就不明显了。